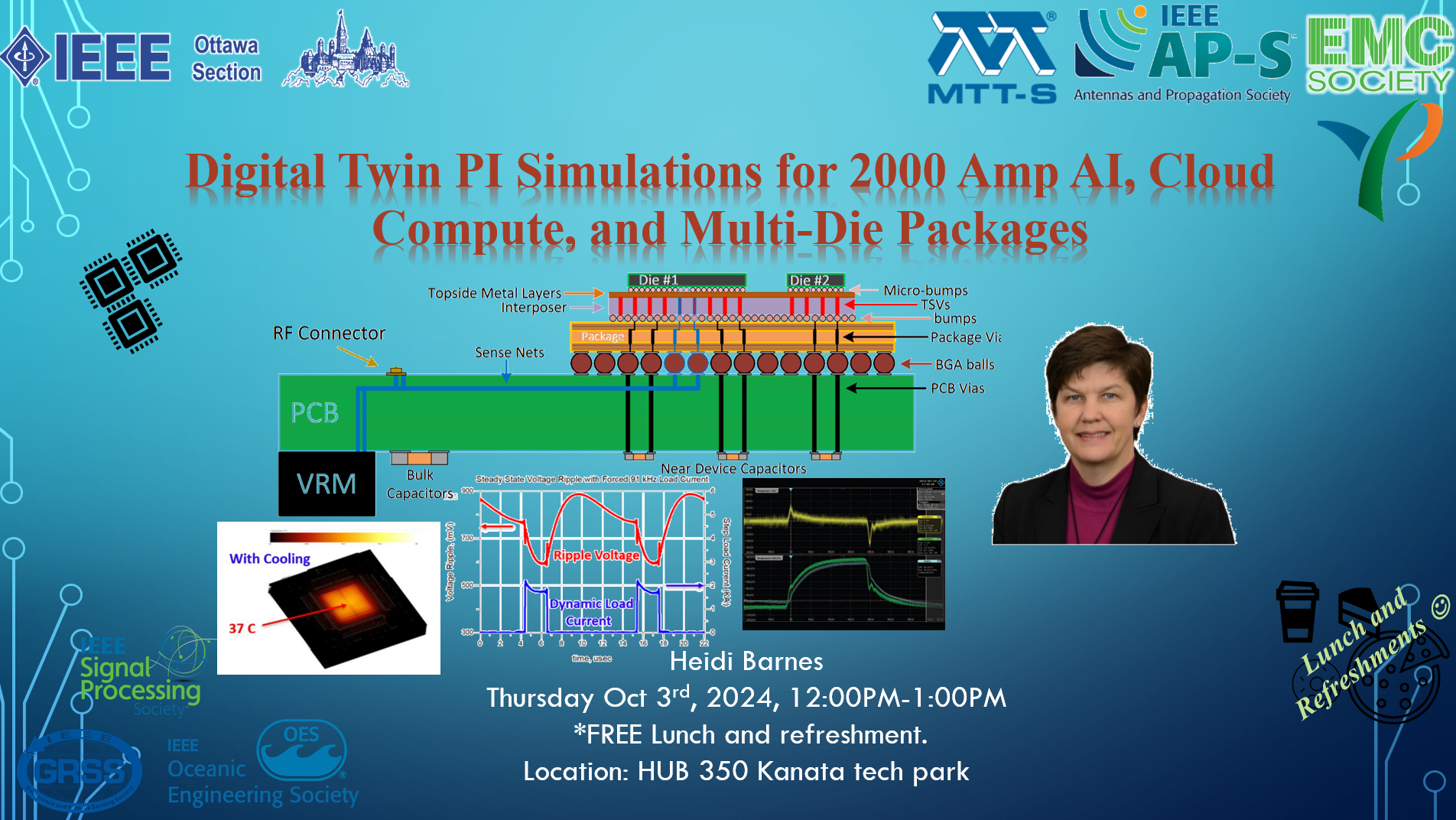

Digital Twin PI Simulations for 2000 Amp AI, Cloud Compute, and Multi-Die Packages

Delivering thousands of amps to the next generation of high-speed digital designs is fast becoming the biggest design challenge for the next generation of custom multi-die packages, AI Chips, and cloud server applications. End-to-end power integrity digital twins with multiphase voltage regulators, PCB PDN with 100’s of capacitors, and dynamic loads are critical for mitigating expensive hardware failures when working with thousands of amps. This presentation will explore the model fidelity trade-offs and lessons learned from simulating the Picotest 2000 Amp Transient Load Stepper demo board with a 55-phase MPS horizontal power delivery topology and over 700 decoupling capacitors.

Constructing and validating the PI digital twin will demonstrate various power integrity simulation tools. EM simulators for DC IR Drop, DC Electrothermal, and AC EM with Decap optimization. Traditional frequency domain analysis with target impedance combined with the Sandler Non-Invasive Stability Margin (NISM) for assessing phase margin helps mitigate resonances by designing for low Q flat impedance. Voltage regulator modeling brings up the challenges of dynamic control loops with small signal and non-linear large signal behavior. Final end-to-end digital twin simulations make use of frequency domain Harmonic Balance simulators to jump directly to steady-state transient power rail ripple for final pass/fail criteria.